从SoC转向Chiplet“小芯片” 延续摩尔定律实现芯片小型化

以英特尔前CEO戈登摩尔命名的摩尔定律,是指集成电路中的晶体管数量每两年翻一番。55年来,半导体行业一直用摩尔定律来制定路线图和研发目标。

为延续摩尔定律、实现芯片小型化,55年间新技术不断涌现,但从历史上看,晶圆的光掩模限制了单个芯片的最大尺寸,芯片制造商和设计人员不得不用多个芯片来完成提供的功能。

很多情况下,甚至是多个芯片提供相同的功能,就像是处理器的内核和内存模块那样。

之前一直在用的SoC(片上系统)技术可以组合不同的模块,模块之间通信速度更快的同时,功耗更低、密度更高,而且成本更低。

但近年来,先进制造节点的成本增加,削弱了SoC技术在成本上的优势。

在最新的台积电2021开放创新平台活动上,Alchip Technologies研发副总裁James Huang表示Chiplet“小芯片”和先进的封装技术,可以提供比单个SoC更有竞争力的成本结构,同时保持接近的性能和功耗。

其引用了两项对小芯片/封装发展至关重要的技术:一项是台积电的 3DFabric和CoWos组合技术,另一项是Alchip的APLink die-to-die (D2D) I/0技术。

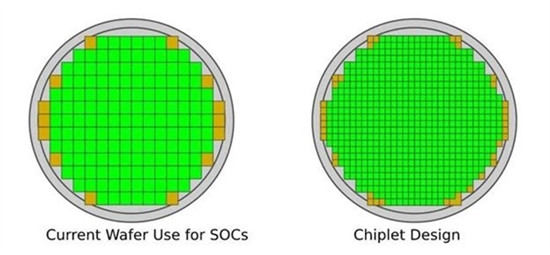

Chiplet“小芯片”技术,顾名思义,就是用多个小芯片封装在一起,用die-to-die内部互联技术,组成异构System in Packages( SiPs)芯片。而更小的芯片单体,可以提高每片晶圆的利用率,从而降低成本。

但为了维持摩尔定律,Chiplet“小芯片”技术还需要提供与SoC技术接近的性能,需要AIchip的APLink D2D I/0技术支撑多个小芯片之间的高速数据流。

APlink 1.0使用的是台积电的12nm工艺,速度是1Gbps;APlink 2.0用的是7nm工艺,速度是4Gbps;正在测试的APLink 3.0已经有16Gbps的速度。

根据路线图,即将推出的APLink 4.0会采用3nm D2D工艺。

APlink 4.0 IP 将支持北/南、东/西方向和对称式PHY对齐,以尽量减少D2D线长,其互连拓扑的I/O总线会用标准的内核电压,PHY宏的速度将达到12Tbps,每条DQ的速度达到16Gbps,且只有5纳秒延迟 。

Chiplet“小芯片”技术涉及封装、EDA、芯片架构设计等多个领域,也有机会重构半导体产业链,但最后落地的关键是商业模式,Chiplet“小芯片”还需要点时间来证明自己。

- IPO丨同星科技今开40.19元/股,上市首日盘2023-05-25

- 英超-福登破门恩西索世界波 曼城1-1战平布2023-05-25

- 苹果cellular版是什么?苹果cellular版可以2023-05-25

- cnc是什么意思?cnc和流水线哪个累?2023-05-25

- 每日报道:塞尔达传说王国之泪吉拉吉拉任务2023-05-25

- 塞尔达传说王国之泪西西摩任务在哪里做2023-05-25

- 雪居之地雪诺博防御怎么样2023-05-25

- 雪居之地雪诺博抓位怎么样_看热讯2023-05-25

- 手机搜索不到wifi是什么原因?手机搜索不到2023-05-25

- ajax怎么实现前后端交互?ajax原理是什么?2023-05-25

- ccd相机属于什么相机?ccd相机可以带上飞机2023-05-25

- 环球速读:一季度宁夏规上新型材料产业企业2023-05-25

- hd什么意思?手机HD怎么关闭?2023-05-25

- 高雄里长参访北京石景山感受大陆发展变化2023-05-25

- 360浏览器打不开是什么原因?360浏览器怎么2023-05-25

- 港股概念追踪 | 夏季用电高峰期将至 火2023-05-25

- iis是什么意思?iis的主要功能是什么?2023-05-25

- 2000亿元产业投资母基金落地 推动先进制造2023-05-25

- 中粮可口可乐否认渠道断货!中粮可口可乐是2023-05-25

- 如何利用跨境电商平台,让你的产品飞入海外2023-05-25

- 微软Teams新增三维虚拟场景,Mesh平台支持2023-05-25

- 618必入好物!韶音OpenFit不入耳耳机为你带2023-05-25

- AMD RX 7600显卡评测解禁:略强于RX 6652023-05-25

- 当前速讯:华为nova11 Ultra荣登京东好物2023-05-25

- 什么是交流电?交流电和直流电有什么区别?2023-05-25

- 成都房价领涨全国,真相是……2023-05-25

- 房企苦日子还没到头:业绩跳水,资产减值,2023-05-25

- 杭州一小时卖地138亿元 民营房企扛起大旗|2023-05-25

- 河南信阳拟调整住房公积金政策:可提取父母2023-05-25

- 咸阳联通荣获陕西省2022年度“通信行业用户2023-05-25

新闻排行

精彩推荐

- 努比亚Z40SPro星空典藏版开售 搭配居中打孔设计

- 首批骁龙8Gen2机型发布时间曝光 11月底两家厂商率先发布

- iQOO11系列最高将配200W快充 10分钟可将4700mAh容量电池充满

- AOC公布CU34G2XP带鱼屏显示器 采用VA面板165Hz刷新率

- 三位知情人士:苹果已暂停几乎所有招聘,直至明年9月

- 荣耀X40琥珀星光配色开售 支持10亿色彩显示

- 小米笔记本Air13翻转本开售 搭载13.3英寸E4OLED屏

- 小米RedmiA70电视开售 采用金属全面屏设计

- 华硕开设首个AI智能工厂 提高产品质量

- 苹果iPadPro2022款/iPad10正式开售 支持ApplePencil悬停功能

综合信息

- 如何利用跨境电商平台,让你的产品飞入海外市场 ?

- 微软Teams新增三维虚拟场景,Mesh平台支持

- 618必入好物!韶音OpenFit不入耳耳机为你带来音乐新体验!

- AMD RX 7600显卡评测解禁:略强于RX 6650 XT 环球今头条

- 当前速讯:华为nova11 Ultra荣登京东好物,4K价位最出色影像手机,618闭眼入

- 喜大普奔!iPhone 15 / Pro无线充电不再受限,这才叫环保

- 小鹏汽车:第一季度营收40.3亿元,同比下降45.9%

- 天天最新:为什么越来越多的OPPO老用户,在更换手机时,不愿考虑OPPO了

- 电池厂商将开启竞争-世界视讯

- 热点评!618红米VS一加:谁更值得?

营业执照公示信息

营业执照公示信息